|

TI的FPD Link III 系列的视频传输桥接器件,是专门用于车载信息娱乐系统以及车载ADAS应用的视频传输桥接器件。通常是串化器与解串器一起配对使用,通过50Ω 单端同轴或 100Ω 差分屏蔽双绞线 (STP) 电缆提供单通道或双通道高速串行数据流,从而简化高速音视频数据远距离传输对线束的要求,并减少车内线束用量。

本文以串化器DS90UB947-Q1,以及解串器DS90UB948-Q1为例,介绍FPD Link III系列器件独有的Test Pattern Generator测试模式生成器。使用该测试模式,可以通过947或者948,使用内部/外部时钟,以及内部/外部timing 参数,来产生纯色/渐变/彩条等测试画面直接显示于屏幕,以辅助判断整个高速视频传输链路的稳定性。  a) 水平黑白渐变 b) 彩条Color Bar 1. 947/948 内部测试模式生成器

947/948内部均带有一个测试模式生成器,能用于对显示面板或者高速链路的调试工作中。该测试模式十分简单且输出测试画面的分辨率以及帧率,均可以通过内部自带的寄存器进行调节,能适用于不同的应用及不同的显示面板调试上。

只要保证947/948的供电稳定,且PDB使能脚可靠拉高,即使此时没有视频信号输入,也能进行显示。如果没有接收到SOC输出的时钟,则可以将测试模式配置为时钟内部的OSC产生显示时钟。而视频的timing参数(HS/VS/DE)既可以使用SOC输出的timing,也可以

使用947/948内部产生的timing参数。测试模式的使能以及相关配置,只需要通过本地I2C,或者远端的I2C设置相关寄存器即可,无需更改外部管脚的配置。

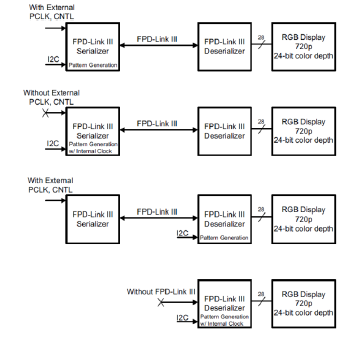

以947/948为例,整个视频链路下共有4种测试模式工作方式: - 通过947产生测试模式图样,并使用SOC产生的PCLK/timing时序

- 通过947产生测试模式图样,并使用947内部自行产生的PCLK/timing时序

- 通过948产生测试模式图样,并使用SOC产生的PCLK/timing时序

- 通过948产生测试模式图样,并使用948内部自行产生的PCLK/timing时序

c) 配置选项

1.1. 视频时序video timing

测试模式下,有两种可选的视频时序模式,分别是外部/内部时序。在 默认的外部时序模式下,测试模式生成器会自动检测由SOC输入的HS/VS/DE视频时序参数,并由此产生相应的相应的时序参数。

而在内部时序模式下,测试模式生成器会根据控制寄存器中配置的分辨率及帧率等参数,产生相应的HS/VS/DE时序参数。

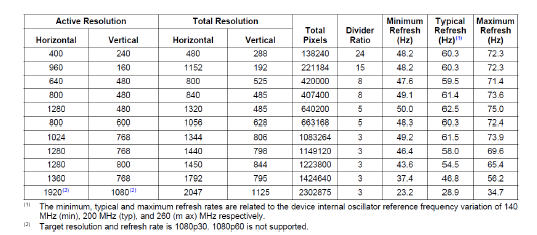

在使用内部时序模式产生测试模式图样时,测试模式生成器可以使用内部OSC产生不同分辨率或帧率下所需的PCLK以及时序参数。这个内部参考的OSC频率典型值是200MHz,带有N=3—63的整数分频器,以产生不同帧率说需要的PCLK。

d) 不同分频系数下的帧率 1.2. 测试图样选择

947/948能提供如下的共16种测试图样。

且947/948可以使能auto-scrolling自动滚动功能,在以下的测试图样中自动循环显示,这个功能可以通过0x65的bit 0 来使能。

i. 纯白色

ii. 纯黑色

iii. 纯红色

iv. 纯绿色

v. 纯蓝色

vi. 水平黑色到白色渐变

vii. 水平黑色到红色渐变

viii. 水平黑色到绿色渐变

ix. 水平黑色到蓝色渐变

x. 垂直黑色到白色渐变

xi. 垂直黑色到红色渐变

xii. 垂直黑色到绿色渐变

xiii. 垂直黑色到蓝色渐变

xiv. 自定义颜色

xv. 垂直彩条

xvi. 颜色反转 2. 测试模式配置寄存器

如果需要输出自定义分辨率或者帧率的测试模式输出的话,需要通过间接寄存器来配置时钟,时序,以及相应的模式。

2.1. 测试模式相关的直接控制寄存器

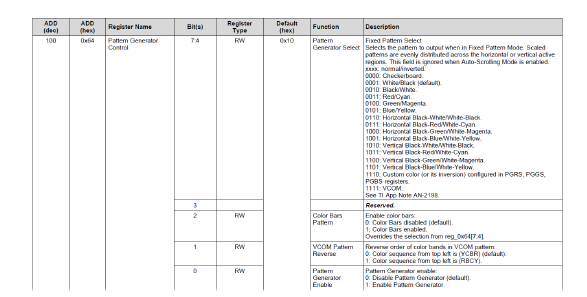

0x64的PGCTL寄存器,以及0x65的PGCFG寄存器是用于配置测试模式的直接控制寄存器。  e) 0x64寄存器 2.2. 间接寄存器

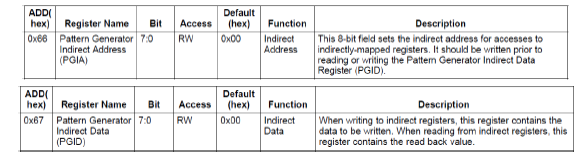

0x66是间接地址寄存器,用于存放需要访问的间接寄存器地址。而0x67是间接数据寄存器,用于存放需要写入间接寄存器的数据。

所以如果要访问间接寄存器,需要先将该间接寄存器的地址写入0x66,然后将数据写入到0x67中,947/948就会自动将该数据写入到该间接寄存器中了。  f) 0x66/67寄存器

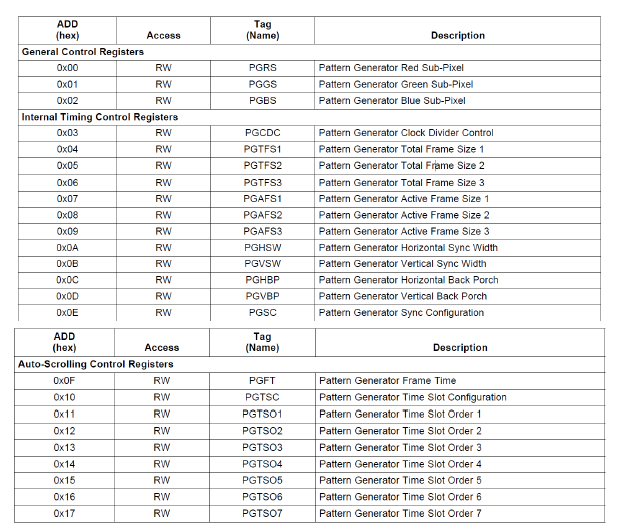

2.3. 间接寄存器表

以下与时序/帧率等自定义参数相关的间接寄存器的读写,都是通过0x66/0x67来进行的。下面简单介绍一下自定义测试模式下所需要配置的相关寄存器。

g) 间接寄存器表

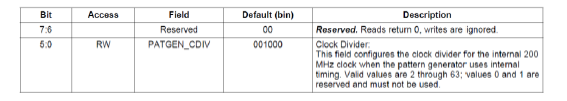

2.3.1. PGCDC: 0x03时钟分频系数控制寄存器

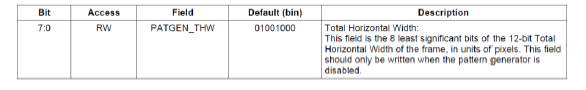

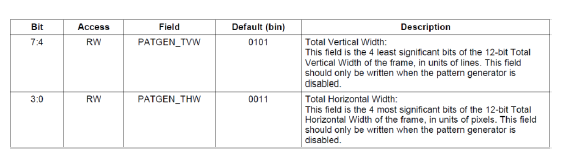

2.3.2. PGTFS1/2/3: 0x04/05/06 总帧大小配置寄存器

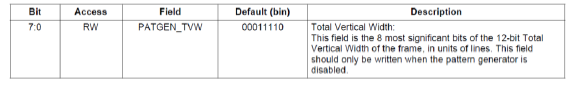

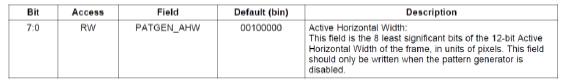

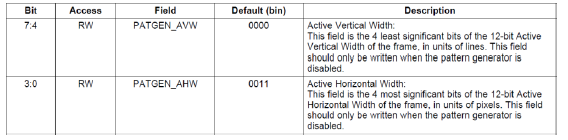

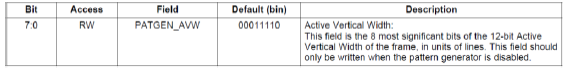

0x04配置的是12 位的总帧水平宽度低8位。  0x05的低4位配置的是12 位的总帧水平宽度的高4位。而高4位配置的是12 位的总帧垂直宽度的低4位。  0x06配置的是12位的总帧垂直宽度的高8位。  2.3.3. PGAFS1/2/3:0x07/08/09 有效帧大小配置寄存器

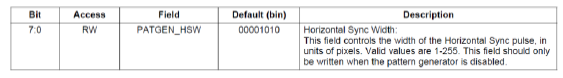

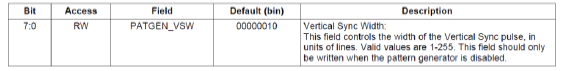

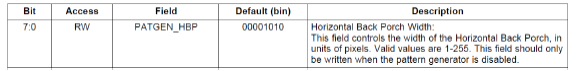

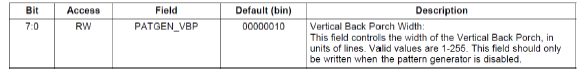

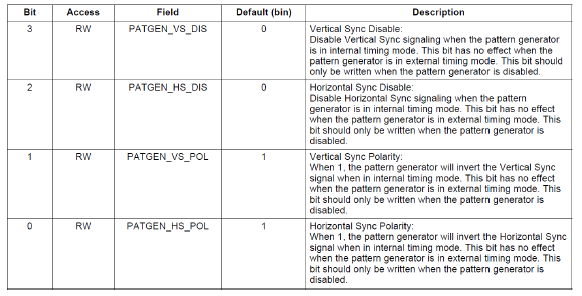

0x07 配置的是12位的有效帧水平宽度低8位。  0x08的低4位配置的是12位的有效帧水平宽度的高4位。而高4位配置的是12位的有效垂直宽度的低4位。  0x09配置的是12位的有效垂直宽度的高8位。  2.3.4. PGHSW:0x0A 水平同步信号宽度该参数只有在内部时序使能的时候才会生效。  2.3.5. PGVSW:0x0B 垂直同步信号宽度,该参数只有在内部时序使能的时候才会生效。  2.3.6. PGHBP:0x0C 水平后肩信号宽度,该参数只有在内部时序使能的时候才会生效。  2.3.7. PGVBP:0x0D垂直后肩信号宽度,参数只有在内部时序使能的时候才会生效。  2.3.8. PGSC:0x0E同步信号配置寄存器  3. 自定义测试模式配置示例

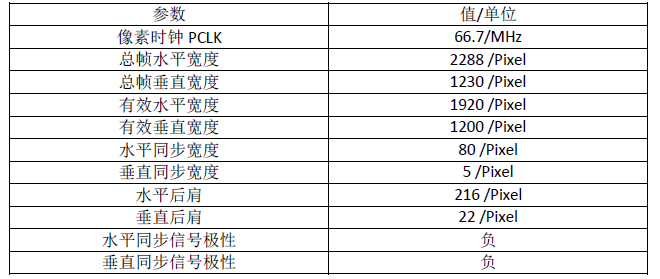

该示例是基于以下的PCLK及timing时序参数来配置自定义分辨率测试模式的:  3.1. 相关寄存器配置

3.1.1. 设置像素时钟PCLK以及总帧大小。

a) 像素时钟PCLK为66.7MHz:写0x03到寄存器0x66,然后写0x03到寄存器0x67,从而设置时钟分频系数为3,200MHz/3 = 66.7MHz

b) 总帧水平宽度为2288,总帧垂直宽度为1230:2288(dec)=0x8F0,1230(dec)=0x4CE。

先写0x04到寄存器0x66,然后写0xF0到寄存器0x67。

写0x05到寄存器0x66,然后写0xE8到寄存器0x67。

写0x06到寄存器0x66,然后写0x4C到寄存器0x67。 3.1.2. 设置有效帧大小:

a) 有效帧水平宽度为1920(0x780),垂直宽度为1200(0x4B0).

先写0x07到寄存器0x66,然后写0x80到寄存器0x67。

写0x08到寄存器0x66,然后写0x07到寄存器0x67。

写0x09到寄存器0x66,然后写0x4B到寄存器0x67。

3.1.3. 设置同步信号宽度:水平同步信号为80,垂直同步信号为5。

a) 写0x0A到寄存器0x66,然后写0x50到寄存器0x67,设置水平同步信号宽度。

写0x0B到寄存器0x66,然后写0x05到寄存器0x67,设置垂直同步信号宽度。

3.1.4. 设置后肩消隐信号宽度:水平后肩宽度为80,垂直后肩宽度为5。

a) 写0x0C到寄存器0x66,然后写0xD8到寄存器0x67。

写0x0D到寄存器0x66,然后写0x16到寄存器0x67。

3.1.5. 使能测试模式生成器

a) 先选定使用内部生成的像素时钟PCLK以及timing时序:写0x04到寄存器0x65。

b) 使能测试模式生成器,并输出彩条图像:写0x15到寄存器0x64。 3.2. 示例代码

以下代码仅为示例代码,0x2C为947的I2C地址,此地址需要与系统上的947实际的I2C地址相匹配。如果要使能948的测试模式,则需要将I2C地址更改为948的地址。

isend -n /dev/i2c1 -a 0x2c 0x66 0x03

isend -n /dev/i2c1 -a 0x2c 0x67 0x03 //200MHz Clock divider, 66.7MHz

isend -n /dev/i2c1 -a 0x2c 0x66 0x04

isend -n /dev/i2c1 -a 0x2c 0x67 0xF0 // least 8 bit of Total Horizontal frame size

isend -n /dev/i2c1 -a 0x2c 0x66 0x05

isend -n /dev/i2c1 -a 0x2c 0x67 0xE8 // Least 4 bit TV + Most 4 bit TH

isend -n /dev/i2c1 -a 0x2c 0x66 0x06

isend -n /dev/i2c1 -a 0x2c 0x67 0x4C // Most 8 bit of Total Vertical frame size

isend -n /dev/i2c1 -a 0x2c 0x66 0x07

isend -n /dev/i2c1 -a 0x2c 0x67 0x80 // least 8 bit of active Horizontal frame size

isend -n /dev/i2c1 -a 0x2c 0x66 0x08

isend -n /dev/i2c1 -a 0x2c 0x67 0x07 // Least 4 bit AV + Most 4 bit AH

isend -n /dev/i2c1 -a 0x2c 0x66 0x09

isend -n /dev/i2c1 -a 0x2c 0x67 0x4B // Most 8 bit of active Vertical frame size

isend -n /dev/i2c1 -a 0x2c 0x66 0x0A

isend -n /dev/i2c1 -a 0x2c 0x67 0x50 // Horizontal Sync Width

isend -n /dev/i2c1 -a 0x2c 0x66 0x0B

isend -n /dev/i2c1 -a 0x2c 0x67 0x05 // Vertical Sync Width

isend -n /dev/i2c1 -a 0x2c 0x66 0x0C

isend -n /dev/i2c1 -a 0x2c 0x67 0xD8 // Horizontal back porch

isend -n /dev/i2c1 -a 0x2c 0x66 0x0D

isend -n /dev/i2c1 -a 0x2c 0x67 0x16 // Vertical back porch

isend -n /dev/i2c1 -a 0x2c 0x65 0x04 //using internal timing and internal clock

isend -n /dev/i2c1 -a 0x2c 0x64 0x15 // Color Bar, enable PG

|  /4

/4

/4

/4