|

中央处理器,也称微处理器(CPU,Central Processing Unit),是微型计算机的运算和指挥控制控制中心。不同型号的微型计算机,其性能的差别首先在于其微处理器性能的不同,而微处理器性能又与其内部结构、组成有关。

CPU从存储器或高速缓冲存储器中取出指令,放入指令寄存器,并对指令译码。它把指令分解成一系列的微操作,然后发出各种控制命令,执行微操作系列,从而完成一条指令的执行。指令是计算机规定执行操作的类型和操作数的基本命令。指令是由一个字节或者多个字节组成,其中包括操作码字段、一个或多个有关操作数地址的字段以及一些表征机器状态的状态字以及特征码。有的指令中也直接包含操作数本身。

CPU依靠指令来计算和控制系统,每款CPU在设计时就规定了一系列与其硬件电路相配合的指令系统。指令的强弱也是CPU的重要指标,指令集是提高微处理器效率的最有效工具之一。

在计算机指令系统的优化发展过程中,出现过两个截然不同的优化方向:CISC技术和RISC技术。CISC是指复杂指令系统计算机(ComplexInstructionSetComputer);RISC是指精减指令系统计算机(ReducedInstructionSetComputer)。这里的计算机指令系统指的是计算机的最低层的机器指令,也就是CPU能够直接识别的指令。随着计算机系统的复杂,要求计算机指令系统的构造能使计算机的整体性能更快更稳定。最初,人们采用的优化方法是通过设置一些功能复杂的指令,把一些原来由软件实现的、常用的功能改用硬件的指令系统实现,以此来提高计算机的执行速度,这种计算机系统就被称为复杂指令系统计算机,即ComplexInstructionSetComputer,简称CISC。另一种优化方法是在20世纪80年代才发展起来的,其基本思想是尽量简化计算机指令功能,只保留那些功能简单、能在一个节拍内执行完成的指令,而把较复杂的功能用一段子程序来实现,这种计算机系统就被称为精简指令系统计算机.即ReducedInstructionSetComputer,简称RISC。RISC技术的精华就是通过简化计算机指令功能,使指令的平均执行周期减少,从而提高计算机的工作主频,同时大量使用通用寄存器来提高子程序执行的速度。

CPU架构是CPU厂商给属于同一系列的CPU产品定的一个规范,主要目的是为了区分不同类型CPU的重要标示。我们日常使用的台式机,笔记本等采用X86架构的处理器,属于CISC范畴,而ARM架构的手机、平板等则属于RISC范畴。

由于CPU内部工作原理内容较多,比较复杂不宜学习并且对于选购CPU没有太大意义,本文主讲和CPU性能有关的参数内容。

x86或80x86是英特尔Intel首先开发制造的一种微处理器体系结构的泛称。该系列较早期的处理器名称是以数字来表示,并以“86”作为结尾,包括Intel 8086、80186、80286、80386以及80486,因此其架构被称为“x86”。由于数字并不能作为注册商标,因此Intel及其竞争者均在新一代处理器使用可注册的名称,如Pentium。现时Intel把x86-32称为IA-32,全名为“Intel Architecture, 32-bit”。 “X86”是Intel和其他几家公司处理器所支持的一组机器指令集,它大致确定了芯片的使用规范。从8086到80186、80286、80386、80486,再到后来的奔腾系列以及现在的多核技术,都是使用一脉相承的x86指令集,既不断扩展又向后兼容。 三十年前,英特尔发布了第一款16位微处理器—8086,当时的著名广告语是:“开启了一个时代”。而当8086的光环退去之后,其支撑架构—我们后来所熟知的x86也成为了最成功的业界技术标准之一。 在8086之后的30年间,x86家族横跨了桌面、服务器、便携式电脑,超级计算机等等。无数对手败在了它的脚下。

目前采用X86架构制造CPU的厂家有三个,INTEL、AMD和VIA,由于VIA制造的CPU性能市场占有率过小,在此忽略VIA的X86架构处理器。

移动版X86处理器和台式机CPU没有本质区别,外观上或许感觉差异较大,但这只是封装形式不同造成,其内部参数性能比较没有本质区别。

台式机CPU

X86的历史

1971 年,英特尔为一家日本计算器厂商制造了英特尔历史上的第一块处理器——4位的4004。很快,在1975年,英特尔又推出了8位处理器8008和8080。 3年以后,16位的8086初次登场。在上世纪80年代初,IBM选择了8086的衍生产品8088作为IBM PC的处理器。IBM的这一举措给x86带来了巨大的发展机遇,并且帮助它成为了行业标准——直到今天。 英特尔执行副总裁Patrick Gelsinger说:“PC行业发展的革命性转折点是1985年32位处理器80386的推出,它推动了整个行业的发展。” 386 之后,19**486诞生了。由于当时数字不能作为商标,英特尔从1993年开始改变了产品命名方法。第五代处理器被命名为Pentium而不是586。 所有的基于x86架构的芯片,开始于8086,一直延续到今天。当然他们的命名发生了变化,运算速度也有了惊人的提升。

X86成功的秘诀

x86为什么能一直成功,击退甚至完全打败其他的处理器架构?从一开始,x86的诞生就可谓生逢其时。1978年,计算机从巨大、昂贵的中型计算机转变为小型、便宜的微型计算机已经有几年了。台式电脑成为变革的前沿。 更重要的是,x86证明了戈登·摩尔在1965年提出的一个定律。戈登·摩尔后来成为英特尔的主席和CEO。摩尔说,在成本不变的前提下,微处理器每过二年其运算速度会翻一番。他的预言后来被称为摩尔定律,30年来始终被证明是有效的。 8086及其后续产品还一直与电脑业的两个大名鼎鼎的名字紧紧联系在一起。1972年,比尔 ·盖茨和保罗·艾伦就尝试用性能很弱的8008开发Basic编程语言,但没有成功。但他们最终在性能强劲一些的8080处理器上开发出了Basic语言,并在1975年把 Basic语言应用到Altair8800 PC。 这成为英特尔和微软亲密关系的开始。微软从那时起,便创造了一个庞大的软件帝国并推动了整个行业的发展。英特尔首席技术官Justin Rattner指出,x86体系架构的灵活性是它过去以及今后成功的关键。他说,虽然人们通常将x86指令集看作是某种一成不变的规范,但是不管是指令集还是体系架构本身,都在过去几年里发生了巨大的变革。Rattner说,x86在上世纪九十年代曾凭借其内置MMX和SSE指令集扩展,一举提高了多媒体和通信应用所需的速度,从而击退了其他专业媒体处理器对它发起的挑战。他还举例说明了x86体系架构在过去几年中新增的一些改进功能。比如在内存管理和虚拟化方面的硬件支持等。 Rattner指出,同样重要的是,英特尔在x86体系架构发展的每一个阶段都保持了向后兼容的特性。指令集的发展以及产品系列内部的兼容性大大扩展了x86体系架构的应用范围,将个人用户与企业用户、便携式电脑和超级计算机都包括了进来。 加州大学伯克利分校的计算机科学教授David Patterson说:“认识到x86体系架构并非一种凝固的设计这一点很重要。30多年来,它们每月都会增加一个说明。现在x86指令集的说明已经达到500多个。每一代都会增加20到100多个。前后兼容很重要,它也一直在增加新的内容。”

X86处理器遵循的原则

1)高性能原则 保证所选购的服务器,不仅能够满足运营系统的运行和业务处理的需要,而且能够满足一定时期的业务量增长的需要。一般可以根据经验公式计算出所需的服务器TpmC值,然后比较各服务器厂商和TPC组织公布的TpmC值,选择相应的机型。同时,用服务器的市场价/报价除去计算出来的TpmC值得出单位TpmC值的价格,进而选择高性能价格比的服务器。 2)可靠性原则 可靠性原则是所有选择设备和系统中首要考虑的,尤其是在大型的、有大量处理要求的、需要长期运行的系统。考虑服务器系统的可靠性,不仅要考虑服务器单个节点的可靠性或稳定性,而且要考虑服务器与相关辅助系统之间连接的整体可靠性,如:网络系统、安全系统、远程打印系统等。在必要时,还应考虑对关键服务器采用集群技术,如:双机热备份或集群并行访问技术,甚至采用可能的完全容错机。 比如,要保证系统(硬件和操作系统)在99.98%的时间内都能够正常运作(包括维修时间),则故障停机时间六个月不得超过0.5个小时。服务器需7×24小时连续运行,因而要求其具有很高的安全可靠性。系统整机平均无故障时间(MTBF)不低于80000小时。服务器如出现CPU损坏或其它机械故障,都能在20分钟内由备用的CPU和机器自动代替工作,无须人员操作,保证数据完整。 3)可扩展性原则 保证所选购的服务器具有优秀的可扩展性原则。因为服务器是所有系统处理的核心,要求具有大数据吞吐速率,包括:I/O速率和网络通讯速率,而且服务器需要能够处理一定时期的业务发展所带来的数据量,需要服务器能够在相应时间对其自身根据业务发展的需要进行相应的升级,如:CPU型号升级、内存扩大、硬盘扩大、更换网卡、增加终端数目、挂接磁盘阵列或与其他服务器组成对集中数据的并发访问的集群系统等。这都需要所选购的服务器在整体上具有一个良好的可扩充余地。一般数据库和计费应用服务器在大型计费系统的设计中就会采用集群方式来增加可靠性,其中挂接的磁盘存储系统,根据数据量和投资考虑,可以采用DAS、NAS或SAN等实现技术。 4)安全性原则 服务器处理的大都是相关系统的核心数据,其上存放和运行着关键的交易和重要的数据。这些交易和数据对于拥有者来说是一笔重要的资产,他们的安全性就非常敏感。服务器的安全性与系统的整体安全性密不可分,如:网络系统的安全、数据加密、密码体制等。服务器需要在其自身,包括软硬件,都应该从安全的角度上设计考虑,在借助于外界的安全设施保障下,更要保证本身的高安全性。 5)可管理性原则 服务器既是核心又是系统整体中的一个节点部分,就像网络系统需要进行管理维护一样,也需要对服务器进行有效的管理。这需要服务器的软硬件对标准的管理系统支持,尤其是其上的操作系统,也包括一些重要的系统部件。

X86 CPU参数讲解

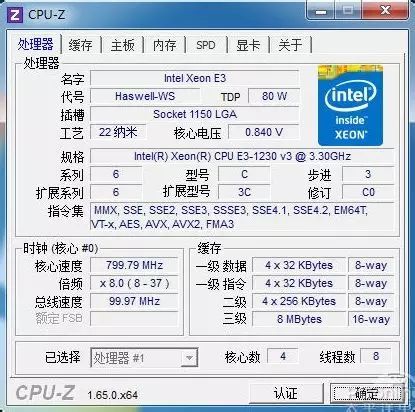

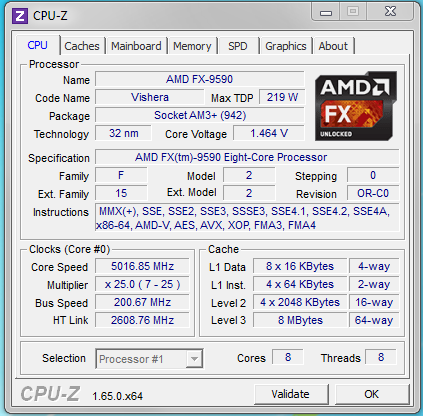

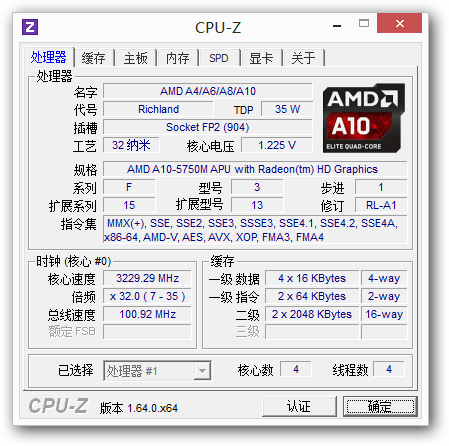

下面以CPU-Z截图为基础,给大家介绍有关CPU的主要参数

上图为Intel至强E3-1230V3处理器的截图

主要包含的参数有以下:

1.型号

2.处理器架构

3.TDP

4.针脚

5.制程/工艺

6.步进

7.指令集

8.频率

9.睿频技术

10.前端总线

11.缓存

12.核心数/线程数

正式发售的CPU均有其自己的型号名称,这也是我们购买CPU时最直接记忆的信息。

CPU-Z提供了两个项目来确定该处理器的型号,一个是“名字”项,一个是“规格”。规格一栏为主板根据CPU内部编号来识别出的相应型号,而“名字”一栏则是CPU根据其他参数规格来推测出的大致型号。

有人会以为这样做岂不是多此一举,其实并不多余。

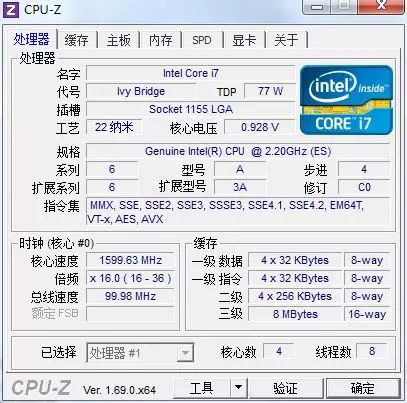

实际上,并非所有CPU都有对应的型号名称,主板仅能识别出内部编号而不能找出对应的型号,这类CPU通常是测试版样品,和正式版CPU参数有时差别较大。这样的CPU用该软件识别时,则会出现如下情况:

处理器型号有一些后缀,比如M,QM(MQ),XM(MX),T,S,TE,E,EQ,K,H(HQ),R,U(UM),Y等。

M代表移动版处理器

QM(MQ)代表四核移动版处理器

XM(MX)代表四核至尊版处理器,AMD的某些MX型号处理器仅为加强版的意思

T、S代表节能版,S还进行了低压处理,节能效果更高

TE,E,EQ代表嵌入式处理器

K代表不锁倍频版,超频专用

H(HQ)代表BGA封装的移动版处理器

R代表BGA封装的台式机处理器

U(UM)代表低压型移动版处理器

Y代表更激进的低压低功耗移动版处理器,面向平板使用

X86处理器微架构

每一代X86 CPU架构是CPU厂商给属于同一系列的CPU产品定的一个规范,主要目的是为了区分不同类型CPU的重要标示。CPU-Z对应的“代号”一栏,即为该处理器采用的架构。这里所指的架构并非大架构(X86)的不同,而是制造商自己更新换代的小架构名称而已。

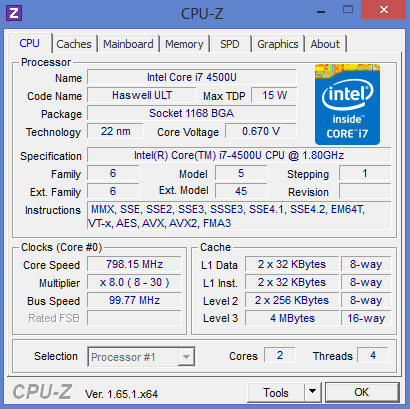

架构决定了该处理器的新旧程度,比如Intel的第二代酷睿i系列架构为Sandy Bridge,第三代架构为Ivy Bridge,第四代架构为Haswell和Crystallwell。

架构后面有时还有子系列,比如DT、MB、ULT、ULX、WS、EP和EX等。DT代表桌面级产品,MB代表移动级产品,ULT、ULX代表低电压产品,WS代表工作站/服务器产品,EP代表High End进阶级产品(通常为服务器最高端级架构),EX代表Extreme Edition至尊级产品。

所以,服务器CPU、台式机CPU、笔记本CPU实际上只是子系列架构的不同而已。

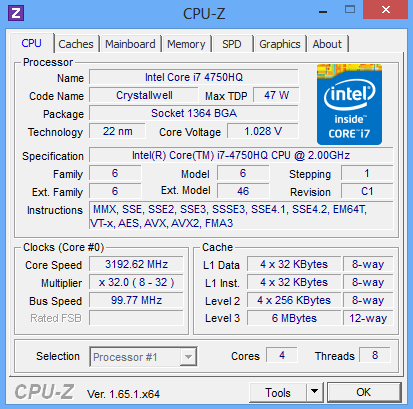

例如:I7-4500U,架构为HASWELL-ULT

TDP

TDP散热设计功耗(TDP,Thermal Design Power)是指正式版CPU在满负荷(CPU 利用率为100%的理论上)可能会达到的最高散热热量,散热器必须保证在处理器TDP最大的时候,处理器的温度仍然在设计范围之内。

但要注意,由于CPU的核心电压与核心电流时刻都处于变化之中,这样CPU的实际功耗(其值:功率W=电流A×电压V)也会不断变化,因此TDP值并不等同于CPU的实际功耗,更没有算术关系。因此,TDP只是一个参考值,用来表征该CPU发热的高低。

随着技术的进步,TDP被赋予了新的意义,其作用在采用了睿频技术的CPU上。台式机由于TDP较大,往往在满载时也不会达到TDP值,而笔记本处理器差异较大。笔记本处理器的TDP普遍在50W以内,而四核处理器有时功耗确实超过了TDP规定的上限。

插槽类型

针脚是CPU与主板的CPU插槽连接的必要部件。CPU-Z上的“插槽”一栏显示的即为该CPU采用的针脚个数及其封装类型。CPU的封装类型分为BGA和PGA两种。

PGA是目前台式机和主流笔记本采用的形式,其主要特点是主板有CPU插槽,和CPU的针脚对应。INTEL在台式机的CPU上将原来的针脚改为触点形式,称为LGA,以避免CPU运输过程中发生针脚折损的问题。PGA还可分成mPGA和rPGA。rPGA未对硅晶顶部加装铝盖,而mPGA则有,避免硅晶因过度挤压受损。mPGA为台式CPU采用(LGA仅是底部针脚形式改变,实际上也属于mPGA),而rPGA为笔记本CPU采用。

BGA是将CPU直接焊接在主板上,以减少CPU和主板之间连接需要的高度,提高机器的集成度,这类CPU通常面向超极本,超薄笔记本和一体机。BGA的CPU由于直接焊接在主板上,想要更换非常困难,需要专业的BGA焊台才能拆下和再次封装。

型号:G3430 插槽:LGA1150

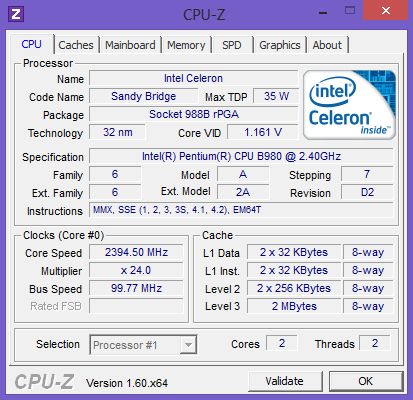

型号:B980 插槽:rPGA988B

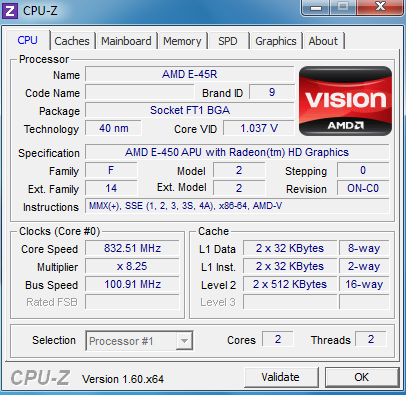

型号:E-450 插槽:BGA FT1

制程工艺

制程工艺就是通常我们所说的CPU的“制作工艺”,是指在生产CPU过程中,集成电路的精细度,也就是说精度越高,生产工艺越先进。

制程的单位是纳米(以前曾用过微米),该数字大小是指IC内电路与电路之间的距离。提高处理器的制造工艺具有重大的意义,因为更先进的制造工艺会在CPU内部集成更多的晶体管,使处理器实现更多的功能和更高的性能;更先进的制造工艺会使处理器的核心面积进一步减小,也就是说在相同面积的晶圆上可以制造出更多的CPU产品,直接降低了CPU的产品成本,从而最终会降低CPU的销售价格使广大消费者得利;更先进的制造工艺还会减少处理器的功耗,从而减少其发热量,解决处理器性能提升的障碍。

计算公式:以当前处理器的制程工艺乘以0.714即可得出下一代CPU的制程工艺,如90*0.714=64.26,即65纳米。

不过,制程提升并非简单,目前制程的发现已经出现瓶颈,INTEL的下一代14nm技术再次延期。未来的制程提升可能会越来越困难。

越新的架构,采用的制程也越新,不过有时为了保证良品率,厂商可能在顶级CPU采用更为成熟的当代工艺,而在低端小规格CPU上采用更先进的新工艺。

最新的INTEL架构Crystallwell采用的是22nm制程工艺

指令集

指令集是存储在CPU内部,对CPU运算进行指导和优化的硬程序。CPU依靠指令来自计算和控制系统,每款CPU在设计时就规定了一系列与其硬件电路相配合的指令系统。指令的强弱也是CPU的重要指标,指令集是提高微处理器效率的最有效工具之一。不同的指令集,对CPU的某些方面产生特定的优化,例如AVX指令集理论上使CPU内核浮点运算性能提升到了2倍。一般说来,指令集支持越多,其CPU执行效率越高。Intel和AMD的CPU指令集不完全相同,因而对每个程序的执行效率也不同。

新架构往往会添加新的指令集支持。在同一代CPU中,为了区分CPU性能高低,也往往在低端CPU上减少对新指令集的支持。

不过,新指令集并不代表会带来性能的提升。新指令集需要相应的程序支持使用,才能得到应用,提高CPU的使用效率。因此,有时候我们并不用担心新指令集的缺少带来的性能损失。

频率

CPU的频率主要包含主频,外频和倍频三部分。

CPU的主频,即CPU内核工作的时钟频率(CPU Clock Speed)。通常所说的某某CPU是多少兆赫的,而这个多少兆赫就是“CPU的主频”。很多人认为CPU的主频就是其运行速度,其实不然。CPU的主频表示在CPU内数字脉冲信号震荡的速度,与CPU实际的运算能力并没有直接关系。由于主频并不直接代表运算速度,所以在一定情况下,很可能会出现主频较高的CPU实际运算速度较低的现象。

主频=外频*倍频,这是X86架构的CPU计算频率的公式。外频是CPU的基准频率,单位是MHz。CPU的外频决定着整块主板的运行速度。倍频系数是指CPU主频与外频之间的相对比例关系。一般情况下,同代(同针脚)的CPU,其外频往往是一样的,只是倍频系数的变化导致主频不同。

为什么会有外频和倍频的区分呢?这个是和CPU的发展有关的,如果大家感兴趣的话可以看最后给出的CPU发展史,这里仅作简单介绍。简单说来,就是CPU发展太快,而其他硬件无法达到同样频率来交互,于是CPU进行妥协,将外频作为和主板之间通讯的频率,而工作频率靠倍频来调节提升。

当下CPU的外频普遍为100mhz,曾经的产品有过最高默认400mhz外频。通常情况下,倍频是有限制的,也就是常说的锁倍频。只有一些工程样品和至尊版处理器或者黑盒版处理器才开放倍频。提高外频和倍频就可以提高CPU的频率,这也就是俗称的“超频”。超频需谨慎,新手不建议超频。

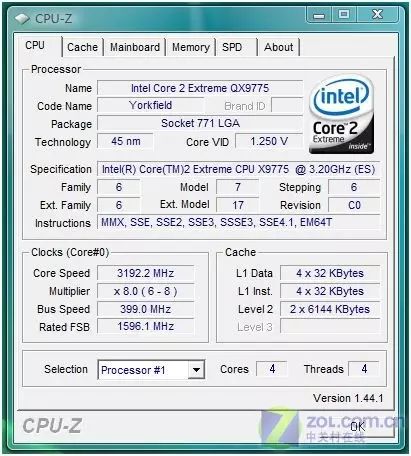

QX9775,默认外频最高的型号

近年来,Intel提出了一个新技术——睿频技术(turbo boost),随后AMD也对其产品增加了睿频技术(turbo core)的支持。实际上这个技术就是对倍频进行增加以达到类似“超频”效果的方式。

睿频技术(turbo boost)

睿频技术是指当处理器的功耗小于TDP而需要较大负载时,可以将倍频进行提高来进行“超频”,使得处理器获得更高的性能,更快的处理数据。

睿频技术最早由Intel提出,在一代酷睿i系列CPU中使用。其前身为Intel Dynamic Acceleration Technology(IDA)技术,在部分酷睿2处理器中使用,IDA技术当时仅是在另一核心休眠时提高该核心的0.5个倍频。而Intel Turbo Boost Technology的运行机制较为复杂。

睿频技术需要参照TDP的大小。当处理器启动睿频后,仍未超过TDP的规定值,则睿频功能继续保持,直至CPU负载减轻到一定数值。此外,如果CPU温度超过了主板设置的阈值范围,也会取消睿频支持。

Intel turbo boost 2.0加入了一些新的机制。TDP被分为两种,短时睿频TDP,长时睿频TDP,此外还有短时睿频时间。短时睿频TDP,是CPU进行睿频加速后的第一个TDP限制值,只要不超过该值,睿频就可以继续进行。如果超过后,睿频就会进行限制,逐渐缩小倍频大小,直至功耗降到TDP范围内。短时睿频时间很好理解,如果超过了这个时间后,处理器就会再次调节睿频的倍频,让TDP下降至CPU-Z中显示的数值。长时睿频其实就是CPU-Z中显示的数值。值得注意的是,一旦超过了主板设定的最高温度,睿频还是会强制停止。

台式机主板可以调节这三项的数值,笔记本中一般都将这些项目隐藏,防止用户将数值调高影响机器发热。

AMD的Turbo CORE技术与英特尔的Turbo Boost技术有着异曲同工之妙,虽然其运作流程不同,但是都是为了在TDP的允许范围内,尽可能的提高运行中核心的频率,以达到提升CPU工作效率的目的。因为AMD没有电源门控(power gating)技术,所以AMD采用P-State电源管理状态切换来达到控制核心功率的效果。举个例子,在一台安装了Phenom II X6 CPU的电脑中,正在运行某个对多线程支持不好,却需要较高频率的程序,使得目前CPU中六个核心中的三个或更多核心没有得到使用,那么Turbo CORE就会启动,将三个空闲核心的频率由默认频率降为800MHz,而另外的三个核心主频会提升500MHz左右。

AMD的Turbo Core 技术虽然在学习“师傅”,但是两点主要的不同看出还没有“出师”,火候未到:

第一:AMD的Turbo Core技术虽然可以将空载核心切换到低速状态,保持在800MHz,但无法全部关闭,因此运行时仍然会有能耗;

第二:AMD的Turbo Core 技术在超频时,并不能针对每个单一的核心进行超频,而是必须在三个以上的核心降频到800MHz的情况下,才能使其他的核心超频,这就大大限制了其超频的能力。而且加速的机会也少得多。 前端总线

前端总线的速度指的是CPU和北桥芯片间总线的速度,更实质性的表示了CPU和外界数据传输的速度。而外频的概念是建立在数字脉冲信号震荡速度基础之上的,也就是说,100MHz外频特指数字脉冲信号在每秒钟震荡一万万次,它更多的影响了PCI及其他总线的频率。之所以前端总线与外频这两个概念容易混淆,主要的原因是在以前的很长一段时间里(主要是在Pentium 4出现之前和刚出现Pentium 4时),前端总线频率与外频是相同的,因此往往直接称前端总线为外频,最终造成这样的误会。随着计算机技术的发展,人们发现前端总线频率需要高于外频,因此采用了QDR(Quad Date Rate)技术,或者其他类似的技术实现这个目的。

FSB是将CPU连接到北桥芯片的总线,也是CPU和外界交换数据的主要通道,因此前端总线的数据传输能力对整机性能影响很大,数据传输最大带宽取决于所有同时传输数据的宽度和传输频率,即数据带宽=总线频率×数据位宽÷8。

以前的CPU曾采用过其他总线,如HyperTransport(AMD)总线、QPI(INTEL)总线。

缓存(Cache)

CPU缓存(Cache Memory)是位于CPU与内存之间的临时存储器,缓存大小也是CPU的重要指标之一,而且缓存的结构和大小对CPU速度的影响非常大,CPU内缓存的运行频率极高,一般是和处理器同频运作,工作效率远远大于系统内存和硬盘。目前的CPU拥有一级、二级和三级缓存(L1 L2 L3 Cache),部分处理器还拥有四级缓存,主要看的是一级和二级缓存大小。注意,Intel和AMD的CPU定义的缓存并不相同,不能直接比较,同品牌不同针脚的CPU一般也不能直接比较缓存来区分性能高低。

一级缓存(L1 Cache)位于CPU内核的旁边,是与CPU结合最为紧密的CPU缓存,也是历史上最早出现的CPU缓存。由于一级缓存的技术难度和制造成本最高,提高容量所带来的技术难度增加和成本增加非常大,所带来的性能提升却不明显,性价比很低,而且现有的一级缓存的命中率已经很高,所以一级缓存是所有缓存中容量最小的,比二级缓存要小得多。

一般来说,一级缓存可以分为一级数据缓存(Data Cache,D-Cache)和一级指令缓存(Instruction Cache,I-Cache)。二者分别用来存放数据以及对执行这些数据的指令进行即时解码。大多数CPU的一级数据缓存和一级指令缓存具有相同的容量,例如AMD的Athlon XP就具有64KB的一级数据缓存和64KB的一级指令缓存,其一级缓存就以64KB 64KB来表示,其余的CPU的一级缓存表示方法以此类推。

二级缓存(L2 Cache)是CPU的第二层高速缓存,分内部和外部两种芯片。内部的芯片二级缓存运行速度与主频相同,而外部的二级缓存则只有主频的一半。L2高速缓存容量也会影响CPU的性能,原则是越大越好,现在家庭用CPU容量最大的是4MB,而服务器和工作站上用CPU的L2高速缓存更高达2MB—4MB,有的高达8MB或者19MB。

三级缓存是为读取二级缓存后未命中的数据设计的—种缓存,在拥有三级缓存的CPU中,只有约5%的数据需要从内存中调用,这进一步提高了CPU的效率。

L3 Cache(三级缓存),分为两种,早期的是外置,截止2012年都是内置的。而它的实际作用即是,L3缓存的应用可以进一步降低内存延迟,同时提升大数据量计算时处理器的性能。降低内存延迟和提升大数据量计算能力对游戏都很有帮助。而在服务器领域增加L3缓存在性能方面仍然有显著的提升。比方具有较大L3缓存的配置利用物理内存会更有效,故它比较慢的磁盘I/O子系统可以处理更多的数据请求。具有较大L3缓存的处理器提供更有效的文件系统缓存行为及较短消息和处理器队列长度。

四级缓存在消费级市场中出现是最近才有的。Intel的Crystallwell架构CPU采用了四级缓存,其本质实际上是eDRAM,给CPU中整合的的核显GT3e使用,当作临时显存。从相关评测中可以看出,这个四级缓存对于核显的性能提升比较显著,但是对于CPU原本的计算则没有影响。未来四级缓存的发展,还需要对市场的进一步观察。

CPU-Z的右下角可以查看CPU的缓存大小,查看四级缓存则需要切换到第二个选项卡“缓存(Caches)”

上图为拥有L4缓存的I7 4750HQ

CPU缓存是和对应型号搭配的,L1和L2都是和核心数成正比,仅L3缓存是低端CPU上进行阉割处理。L3主要影响部分游戏性能,但也不是很大。

核心数/线程数

多内核是指在一枚处理器中集成两个或多个完整的计算引擎(内核)。多核处理器是单枚芯片(也称为“硅核”),能够直接插入单一的处理器插槽中,但操作系统会利用所有相关的资源,将它的每个执行内核作为分立的逻辑处理器。通过在两个执行内核之间划分任务,多核处理器可在特定的时钟周期内执行更多任务。

多核心技术需要系统和软件的支持。windows2000以后的系统提供了多核心的支持,而之前的win me和win98等则仅支持单核。现阶段大部分程序都只是不超过4核心的优化支持,超过4核后性能提升不明显。

一般来说,线程数等于核心数。但Intel为了更充分的利用CPU资源,开发了超线程技术。

HT超线程技术,也就是Hyper-Threading,是Intel早在2001年就提出的一种技术。尽管提高时钟频率和缓存容量可以改善CPU的性能,但是受到工艺和成本的限制,CPU无法无限的提升参数来提升性能,实际上在应用中基于很多原因,CPU的执行单元都没有被充分使用。

为此,Intel则采用另一个思路去提高CPU的性能,让CPU可以同时执行多重线程,就能够让CPU发挥更大效率,即所谓“超线程(Hyper-Threading,简称“HT”)”技术。超线程技术就是利用特殊的硬件指令,把两个逻辑内核模拟成两个物理芯片,让单个处理器都能使用线程级并行计算,进而兼容多线程操作系统和软件,减少了CPU的闲置时间,提高的CPU的运行效率。目前的多线程技术一般采用多个微理器即多处理器结构,线程与处理器形成一一对应关系。而英特尔Hyper-Threading技术的特点是:

(1)物理上用一个处理器处理多个线程

(2)多线程的分配采用根据计数器的空闲状态进行线程处理的SMT(simultaneous multi-threading)方式。

HT技术最早出现在2002年的Pentium4上,它是利用特殊的硬件指令,把两个逻辑内核模拟成两个物理芯片,让单个处理器都能使用线程级并行计算,进而兼容多线程操作系统和软件,减少了CPU的闲置时间,提高CPU的运行效率。但是,由于这个设计太过超前,奔腾4并没有借助HT大放光彩,在之后的酷睿架构中,Intel也再没有使用这个技术。然而,基于Nehalem架构的Core i7再次引入超线程技术,使四核的Corei7可同时处理八个线程操作,大幅增强其多线程性能。

现在的HT技术很成熟,超线程技术带来的效率提升可达30%之多。不过对于一般的程序来说,超线程带来的提升或许很小,尤其是超过了四线程之后。

Tick-Tock Tick-Tock是Intel公司发展微处理器芯片设计制造业务的一种发展战略模式,在2007年正式提出。 “Tick-Tock”的名称源于时钟秒针行走时所发出的声响。Intel指,每一次“Tick”代表着一代微架构的处理器芯片制程的更新,意在处理器性能几近相同的情况下,缩小芯片面积、减小能耗和发热量;而每一次“Tock”代表着在上一次“Tick”的芯片制程的基础上,更新微处理器架构,提升性能。一般一次“Tick-Tock”的周期为两年,“Tick”占一年,“Tock”占一年。Intel指出,每一次处理器微架构的更新和每一次芯片制程的更新,它们的时机应该错开,使他们的微处理器芯片设计制造业务更有效率地发展。

Tick-Tock模式就是每隔两年就会推出新的制程技术,然后隔年推出新的微构架,如英特尔在2005年推出65nm工艺酷睿处理器以及酷睿微构架,2007年推出的45nm工艺Penryn处理器以及2008年Nehalem微构架,以及在2009年推出的32nm工艺Westmere处理器和2010年Sandy Bridge微构架,都是符合Tick-Tock研发模式。Tick-Tock研发模式将处理器技术不断推向新的高度,也是英特尔保持活力和市场占有率的重要战略。 Intel现在的处理器开发模式是“Tick-Tock”,也是每两年更新一次微架构(Tock),中间交替升级生产工艺(Tick)。Nehalem是采用45nm工艺的新架构,而2009年的Westmere将升级到32nm,2010年的Sandy Bridge又是新架构。最新情报显示,Intel将在2012年4月推出“IVY Bridge”,也就是Sandy Bridge的22nm工艺升级版;2013年再推出“Haswell”,基于22nm工艺的又一个新架构。 现在已经可以基本确定Intel 22nm之后的下一站将停留在15nm,已经有很多证据证明了这一点,据说台积电也是如此,不过也有说法提到了16nm、14nm等不同节点,而且IBM/AMD的规划就是16nm。再往后应该就是11nm,不过Intel也曾在不同场合提及过10nm,看来遥远的未来仍然充满了未知数。 代号方面之前有人说2013年的22nm Haswell后边是应该是Rockwell,按惯例架构不变、工艺升级,不过SemiAccurate网站今天曝料称,其实真正迈入后20nm时代的将是“Broadwell”,再往后工艺不变、架构革新的将是“SkyLake”(另一说Sky Lake),届时甚至可能会集成源于Larrabee项目的图形核心,当然前提是Intel能够真正找到充分发挥x86架构图形效率的门路。 还要往后?那我们再说一个名字“Skymont”。可以预料,到时候又会升级工艺了,按照现在的初步规划将会是11nm,但怎么着也得是2016年的事情了。 65nm Merom - Tock 45nm Penryn - Tick 45nm Nehalem - Tock 32nm Westmere - Tick 32nm Sandy Bridge - Tock 22nm Ivy Bridge - Tick 22nm Haswell - Tock 14nm Broadwell - Tick 14nmSkylake- Tock 11nm Skymont(平台代号) - Tick

|  /3

/3

/3

/3