|

摘要: 目前,基于ARM和FPGA架构的嵌入式系统在通信设备中得到广泛的应用。文章提出了一种基于ARM和FPGA的环形缓冲区接口设计方案,从而实现了ARM和FPGA之间的数据缓冲和速率匹配。实际测试表明该方案能够有效地对数据速率进行匹配,且具有良好的可扩展性。

关键词:ARM;现场可编程门阵列;环形缓冲区

0 引言

随着嵌入式系统、软件无线电和无线通信的发展,基于嵌入式系统和软件无线电的实现架构广泛应用到无线通信设备中。其中,采用ARM+FPGA的软件无线电体系结构来实现的通信设备是最近十分流行的一种方案。该方案充分利用ARM CPU灵活便捷的优势,用来处理用户输入、系统控制、网络协议功能,而利用FPGA卓越的实时信号处理优点,对无线通信的物理层信号进行无线收发处理。在这种体系结构中,ARM和FPGA的数据通信信号接口设计是其中十分关键的一个环节。由于无线设备的数据收发往往具有一定的突发性,在高速数据收发情况下,需要设计一种合理的缓冲区进行数据传输速率的匹配和缓冲。另外,对于ARM CPU来说,由于CPU往往需要同时并行处理多种任务,如何尽可能地保证数据的实时接收,也是设计中的一个关键。本文提出了一种基于ARM和FPGA的环形缓冲区设计结构,能可靠有效地处理好两者之间数据传输速率匹配和缓冲,且具有很好的扩展性。

1 缓冲区接口硬件设计

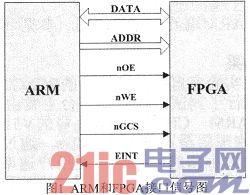

本方法设计的硬件接口如图1所示。FPGA作为一个存储器外设与ARM连接,采用的是标准的总线接口,由nGCS片选线、双向数据线DATA、地址线ADDR、以及读写控制线nOE和nWE等信号线组成。另外,EINT是中断信号线,FPGA发起中断向ARM请求处理。

2 缓冲区接口软件设计

为了设计ARM和FPGA的缓冲区接口,首先要利用图1中的信号线实现ARM对FPGA的基本读写操作,这需要双方遵循拟定的接口时序相互配合进行,这可以通过参考相应的ARM内核CPU用户手册,在FPGA端编写相应的接口代码来配合ARM CPU2端的读写时序实现。

下面重点介绍环形缓冲区接口的软件实现。

2.1 缓冲区空间设计

如上所述,FPGA是作为ARM的一个存储器外设来设计的。在本方案中,FPGA存储器空间包括两个部分:寄存器空间和数据缓冲区空间。

寄存器空间用于设置各种读写的参数,包括缓冲区读写指针、缓冲区忙闲状态等;而缓冲区用于大量数据的临时存储,按作用分为发送缓冲区和接收缓冲区。设计中对所有空间都采用统一编址方式实现,利用ARM与FPGA之间相连的接口地址线(ADDR)的最高两位来区分,例如,00表示寄存器空间,01表示发送缓冲区空间、10表示接收缓冲区空间,11为保留。

在本文的环形缓冲区结构设计中,发送(接收)缓冲区又分为若干大小相同的子缓冲空间,这些子缓冲空间共享同一个地址空间,由FPGA内部的缓冲区忙闲指示寄存器和子缓冲空间的控制指针来引导ARM对子缓冲区的读写。子缓冲空间的控制指针循环依次变化,数据帧也循环依次写入指针指向的子缓冲空间或被读走,这样就构成了环形缓冲区。

以实际项目的设计为例,发送(接收)缓冲区分别由16个子缓冲空间组成,每个子缓冲空间的大小为256双字节,这16个子缓冲空间共享一个地址空间。设计中的接口地址线一共为10位,数据线是16位。每个数据帧的最大长度也设置为256双字节,以便一个缓冲区能够装满一个帧,简化缓冲区管理。以发送缓冲区为例,其结构设计如图2所示。

尽管设置了16个子缓冲空间来应对可能的突发数据流,为了防止ARM将所有的子缓冲区写溢出,在FPGA内部设置了缓冲区忙闲寄存器指示,当所有的子缓冲空间都写满后,缓冲区忙闲指示寄存器设置为忙。

2.2 发送程序设计

首先介绍数据的发送过程,也就是数据帧从ARM到FPGA的发送流程。程序分为两个部分,一个是ARM端的程序,负责将来自用户的数据组成最大不超过256双字节的数据帧,然后向FPGA内部的发送缓冲区写数据帧;另外一个是FPGA端的程序,负责将接收的ARM数据帧写入发送缓冲区,同时将各个子缓冲空间的数据依次提取出来,传递给物理层进行发送。

发送部分ARM端的程序流程图如图3所示。将用户数据首先组装成规定大小的数据帧,然后判断发送缓冲区是否有空闲的子缓冲空间,若发送缓冲区满则等待,否则将数据帧发送到统一编址的发送缓冲区空间。

发送部分FPGA端的程序流程可分为接收ARM写入的数据帧和将发送缓冲区中的数据帧发送给物理层进行数据处理。这两部分的程序流程分别如图4和图5所示,主要是利用子缓冲空间的忙闲状态与读写指针的变化来控制数据帧的读取和写入,实现子缓冲空间循环利用以及数据帧的正常发送和缓存。

2.3 接收程序设计

数据的接收同样包括ARM端和FPGA端两部份程序,相互配合共同完成ARM从FPGA读取数据帧的流程。FPGA端的程序主要有两个任务,一是负责把从物理层接收到的数据帧写入接收缓冲区中,并向ARM发出中断请求接收数据帧,另一个是在得到ARM接收完毕确认后处理好接收缓冲区的空间释放;ARM端的程序负责从FPGA接收缓冲区中读取数据帧。

接收部分FPGA端仍然是利用子缓冲空间的忙闲状态与读写指针的变化来控制数据帧的写入和读取,并实现接收完来自物理层数据帧后向ARM发出发起中断,当ARM读取数据帧后释放子缓冲区空间,程序结构如图6和图7所示。

接收部分ARM端的程序流程如图8所示,当ARM接收到FPGA的中断后,判断是否有数据帧要上传,若不是则不做任何处理;若是则从统一编址的接收缓冲区读取数据帧,然后向FPGA发出接收完毕指示以便于FPGA及时释放相应的子缓冲空间。

3 测试结果

本方案在实验室自行开发设计的BCNG2440宽带无线收发平台上进行了测试运行。该平台主要由Samsung公司S3C2240型的ARM CPU和Xi-linx公司的V5系列SX95T型FPGA组成。物理层最高速率为1Mb/s,通过变化来自应用层的数据包大小和的间隔来改变用户速率,用以测试

ARM和FPGA的数据缓冲区和匹配功能。实际测试和运行表明,此方案是有效而合理的。

以发送缓冲区设计为例,图9给出了用chipscope观察该部分设计方法的正确性。ARM发送数据帧到发送缓冲区后FPGA的内部变化如图7所示。可以看到ARM发送的数据帧写入了FPGA中序号为13的子缓冲空间,结束时写指针(nTxBuffWNum)递增指向了序号为14的子缓冲空间,同时序号为13(实际上是第14个,这是由于序号是从0到15)的子缓冲空间被标示为占用。从图中也可以看到前面写入的数据帧已经发送,其它子缓冲空间都为空闲状态,读指针(nTxBuffRNum)也是正常变化的。

应该指出的是,本方案具备良好的扩展性。通过改变子缓冲区的数目和子缓冲区的大小,可以用来对不同的应用情况进行速率匹配。

4 结语

本文介绍了基于ARM和FPGA的环形缓冲区的设计方法,实现简单并便于扩展。测试结果表明此方法能实现ARM和FPGA之间数据的有效传输。对网络协议的实现具有重要的参考价值。 |  /4

/4

/4

/4