看到国产fpga已经能达到spartan6和kintex7的水平很欣慰,接着上一章继续深入学习logos系列fpga内部结构。上一篇介绍了基本逻辑单元,现在开始讲乘法器,如果说逻辑单元结构紫光同创更接近spartan6,区别在于使用lut5,那么乘法器则更加接近于xilinx的dsp48A1。

logos的乘法器叫APM 内部结构如下所示

A.I/O 单元

1.实现数据输入/输出寄存。

2.各个寄存器的 CE 信号(高有效)和 RST 信号(高有效)都有其各自独立的 CE 和 RST输入来控制。RST 异步/同步性质由共享参数 ASYNC 决定。

3.模式端口按逻辑归属分成三组 MODEX,MODEY[2:0],MODEZ[3:0]。每组模块控制由各自的独立的 REG,RST,CE 参数控制。 4.实现 APM 正向级联(PO=>PI,XO=>XI)和反向级联(XBO=>XBI)。APM 级联用于实现滤波器以及高位宽乘法器如 36*36。

5.实现对常数输入和重复的符号位简化接线。

B. 预加单元

1.硬件实现为 18+/-18,输出 18 位结果;或两个 9+/-9,各输出 9 位结果(当 SIMD=1)。

2.结果的符号性(signedness)由软件判定并存放在 XSIGNED 参数中,供乘法单元使用。

3.在 18 位运算模式下,为确保结果无溢出(符号性判定正确),软件里需限制最大输入位宽为 17 位(即无符号数 bit[17]=0,有符号数 bit[17]=bit[16]);当一个输入为无符号数而另一输入为有符号数时,无符号数的有效位数需进一步缩小为 16 位(即 bit[17]=bit[16]=0)。在 9 位运算模式下(SIMD=1),为确保结果无溢出(符号性判定正确),软件里需限制最大输入位宽为 8 位(即无符号数 bit[8]=0,有符号数 bit[8]=bit[7]);当一个输入为无符号数而另一输入为有符号数时,无符号数的有效位数需进一步缩小为 7 位(即 bit[8]=bit[7]=0)。

4.仅当 unsigned + unsigned 情况下,Preadder 输出结果为 unsigned(XSIGNED=0),其余情形的 Preadder 结果均判定为 signed (XSIGNED=1)。

5.Preadder 可被旁路(PREADD=0)。

C. 乘法单元

1.实现一个 18*18,结果带符号扩展为 48 位;或两个 9*9(当 SIMD=1),9*9 结果带符号扩展为 24 位。

2.X/Y输入操作数的符号性(signedness)由参数XSIGNED/YSIGNED决定,该参数为两个9*9乘法器共享。

D. 累加单元

1.实现一个 48 位加减法/累加器;或两个 24 位加减法/累加器(当 SIMD=1),两者共享一个 carryin(进位)。 2.Postadder 的两个主要输入端为乘法器和 Zmux,两者之一可任选取负值。

3.为减少 APM 端口数,节约布线资源,Z 端口高 18 位也可以为 Preadder 所复用,原则上Postadder 此时不应再从 Z 端口取操作数。

4.Postadder 可被旁路(当 POSTADD=0),此时 APM 输出乘法器结果。

xilinx的dsp48A1 slice的结构则如下图

仔细研究数据通路会发现两者结构并没有相差很大 通过两个加法器和一个乘法器的路径基本一致

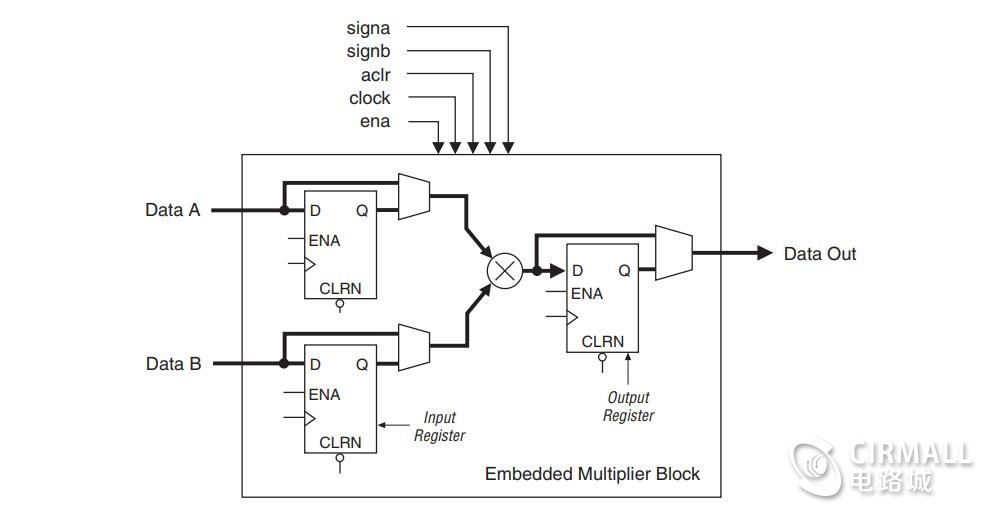

cyclone iv的乘法器则如下所示

也不难看出logos系列乘法器的表现会优于C4.

乘法器讲完再到内存控制器,相比如cyclone iv只能支持到ddr2,logos系列再一次超越c4,和spartan6达到了ddr3的级别。

HMEMC是Logos 系列FPGA芯片所拥有的高性能嵌入式硬核内存控制器,他支持LPDDR,DDR2,DDR3。支持x8,x16 DDR存储器。 支持标准的AXI4总线协议。HMEMC主要由 DDR Controller 和 DDR PHY 组成。DDRC 模块主要对用户读写请求进行仲裁,完成 AXI4 命令到 DFI 读写命令和操作时序的转换,同时对 DDR 存储器读写操作进行调度。DDR PHY 完成不同类型的 DDR 存储器的初始化,完成 DDR3 的 write leveling,完成不同 DDR类型的 DQS gate training 以及 read data eye leveling 等工作。接收 DDRC 发送的 DFI 命令并进行协议转换后发送到 DDR 存储器。除此之外,为了能使 HMEMC 正常工作,还需要初始化和复位模块,负责整个系统上电初始化和所有模块的复位控制。为了减少风险,这部分功能放在 FPGA fabric 里,通过软逻辑来实现。

再谈片内ADC,做单片机开发或者FPGA开发应该都不会陌生。单片机都会带有一个片内ADC,高端的FPGA由于高频工作发热太大,一般也会带有ADC用作芯片温度检测,多出来的通道,用户可以任意发挥。altera在max10系列中嵌入了ADC单元,logos也同样加入了同样的设计,可见logos真是集百家之所长。

Logos 系列 FPGA 产品提供了 ADC 资源,每个 ADC 带有 12 个 Channels,其中有 10 个模拟输入引脚与 GPIO 复用,另 2 个是专用模拟输入引脚,这 12 个 Channels 的扫描方式由 FPGA 灵活控制,用户可以通过 User Logic 读写 ADC 的控制寄存器,配置 ADC 的工作模式和通道选择等,通过读 ADC的状态寄存器,获取 ADC 通道的转换结果和用来校准的 offset 和 gain error 值等。

ADC的参数如下图:

分辨率:12-bit

采样率:1MSPS,12 个通道,其中有 10 个模拟输入通道与 GPIO 复用,2 个是专用模拟输入通道;

ADC 内部及外部参考电压 VREF 为 2.5V;

集成温度传感器,精度范围在±4℃;

offset 误差为±1.1LSB;

gain 误差为±0.2LSB;

信噪比(SNR): 71.7dB;

微分非线性(DNL)为±0.5LSB;

积分非线性(INL)为±0.5LSB;

而MAX 10 内部集成的12bit SAR ADC的特点为:采样速率1Mhz,模拟通道多达18个,单个ADC多达17个,双ADC器件中有16个双功能ADC通道,2个专用的ADC。可见max系列通道稍微多一些,但是性能两者相差不大。

|  /4

/4

/4

/4