刚刚开始接触FPGA的时候,只要一提到 FPGA 大家的脑海种可能就出现那几家,Xilinx、Altera,玩的时间长的可能还知道actel、lattice、microsemi,国家重点支持的CPU、DSP 、存储器都取得了一定的技术突破,似乎只有FPGA还没有大规模国产化,想买一颗国产的CPLD也不是一件容易的事,完全想不到不出10年已经可以用上国产FPGA的开发板,正好趁着论坛给的好机会近距离欣赏PGL12G开发板。

这块板子其它小伙伴应该也介绍得差不多了,外设很丰富,接口全,大家也都不陌生,这次我的重点就是这最中间的PGL12G。 这款FPGA是属于LOGOS系列,按照官网的介绍,Logos系列FPGA采用40nm CMOS工艺和全新LUT5结构,集成RAM、DSP、ADC、Serdes、DDR3等丰富的片上资源和IO接口,具备低功耗、低成本和丰富的功能,广泛应用于工业控制、通信、消费类等领域。

从介绍来看,这系列型号应该是用于替换采用Altera cyclone iv和Xilinx spartan 6的成本敏感型项目,为客户提供更高的性价比,从制程来说,cyclone iv是基于优化的 60 纳米低功耗制程技术构建,spartan 6是基于低功耗45nm、9金属铜层、双栅极氧化层工艺技术,毕竟这两款芯片面世也有十余年,logos系列是有后发制程优势的。相当于以上两块使用范围更为广泛的芯片来说,logos目前产品种类的封装还不是特别丰富,C4和S6都是有从几K的逻辑资源到150K的跨度,logos的高容量还在研发之中。

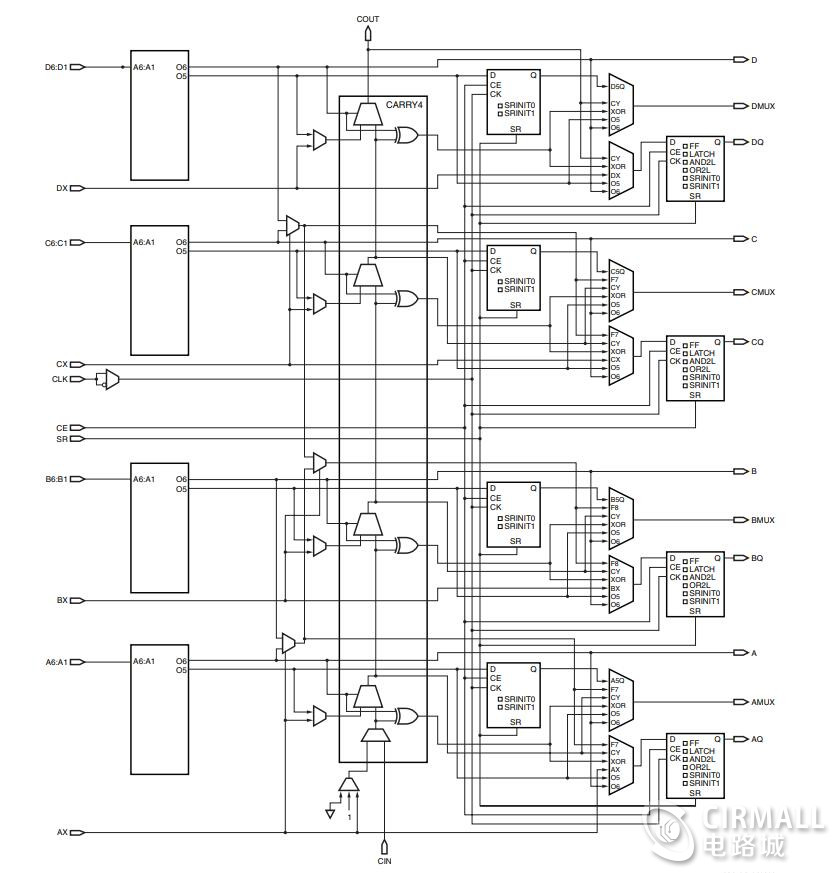

制程聊完了,那么再看看这三款FPGA芯片在架构实现上又有什么不同的考量。学FPGA大家都是知道一本教程前几章基本都是先讲FPGA的历史,然后就是剖析内部结构了。SPARTAN6的逻辑模块叫可配置逻辑块(CLB),CYCLONE IV的逻辑模块叫逻辑阵列模块(LAB),LOGOS最基本的逻辑资源叫可配置逻辑模块(CLM),它主要由多功能 LUT5,寄存器以及扩展功能选择器等组成。CLM 在 Logos 系列产品中按列分布,支持 CLMA和 CLMS 两种形态,其分布比例为 3:1。CLMA 和 CLMS 均可实现逻辑、算术、移位寄存器以及ROM 功能,仅有 CLMS 支持分布式 RAM 功能。CLM 与 CLM 之间,CLM 与其它片内资源之间通过信号互连模块联结。CLM 的使用可通过深圳市紫光同创电子有限公司的软件 Pango Design Suite 来完成。CLMS 还可通过 Pango Design Suite 内嵌的 IP Compiler 工具生成分布式 RAM IP。CLMA 的逻辑框图如下所示,每个 CLMA 包含 4 个 LUT5A、6 个寄存器、多个扩展功能选择器、以及 4 条独立的级联链等。其中 LUT5A 采用了创新的架构设计,在 5 输入查找表的基础上集成了专用电路以实现 4:1 多路选择器功能和快速算术进位逻辑;扩展功能选择器主要用于实现宽位查找表和输出选择功能;级联链包括算术逻辑进位链(从 CIN 到 COUT),专用移位寄存器链(从 SHIFTIN到 SHIFTOUT),寄存器复/置位级联链(从 RSIN 到 RSOUT)和寄存器 CE 级联链(从 CEIN 到 CEOUT)。此外,相邻的两个 CLM 之间还有一条基于 LUT7(从 L7IN 到 L7OUT)的专用级联链,用于组合生成 LUT8。LUT5A 和 LUT5S 可灵活配置,以支持基本逻辑,多路选择,算术逻辑,ROM 功能以及分布式RAM 功能(仅限于 LUT5S)等不同功能。在逻辑功能模式下,每个 LUT5A(或 LUT5S)可实现 1 个 LUT5,结合扩展功能选择器,每个CLM 可支持实现 2 个 LUT6、1 个 LUT7 或与相邻 CLM 组合实现一个 LUT8。利用 LUT7 专用级联链,每 2 个 CLM 可支持为 1 个 32:1 多路选择器。更宽的多路数据选择可通过 CLM 组合产生。 在算术功能模式下,LUT5A(或 LUT5S)可实现加减法运算;计数器;比较器;快速异或逻辑运算以及宽位与逻辑运算等。 在 ROM 模式下,LUT5A(或 LUT5S)可以用作 32*1 ROM,还可以通过内置的扩展功能选择器进行深度级联。ROM 数据的初始化在编程配置过程中完成。

CLMS 是 CLMA 的扩展,它在支持 CLMA 所有功能的基础上增加了对分布式 RAM 的支持,其中的多功能 LUT5 称为 LUT5S。CLMS 可配置为大小为 16*4 的 SP (Single Port,单口) RAM 或大小为16*4 的 SDP (Simple Dual Port,简单双口) RAM。CLMS 的逻辑框图如下所示:

从底层结构来说logos的设计更加接近spartan6,为什么这么说呢,下面介绍下spartan6和cyclone iv的结构。

Spartan-6每个CLB模块里包含两个SLICE,Slice就是通过LUTS以及Carry Logic和Multiplexers之间的互连来形成组合逻辑,再通过Storage elements构成寄存器以形成时序逻辑。同时借助SLICEM的LUTS,还可以构成RAM,ROM,Shift Registers资源。CLB通过交换矩阵和外部通用逻辑阵列相连,像logos把clm分成clma和clms,XILINX也把slice分成sliceM和sliceL,结构如下。 SLICEM

SLICEL

这么看下来是不是觉得两者架构思维相似,再看下cyclone iv的LAB,LAB实际上就是16个LE的组合,逻辑单元 (LE) 在 Cyclone IV 器件结构中是最小的逻辑单位。LE 紧密且有效的提供了高级功能的逻辑使用。每个 LE 有以下特性:一个四输入的查找表 (LUT),以实现四种变量的任何功能,一个可编程的寄存器,一个进位链连接,一个寄存器链连接,LE的结构如下图所示:

查找表LUT(Look-Up-Table)其本质是一个静态存储器SRAM,目前FPGA多采用4或者6输入的LUT,每个LUT可以看作一个有4位地址线的16x1的RAM。当我们通过原理图或HDL语言描述了一个逻辑电路后,FPGA开发软件会自动计算逻辑电路的所有可能的结果,并把结果事先写入RAM。这样,在FPGA工作时,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出。 看完这些结构,我们可以知道其实在逻辑资源描述最精确的是altera,芯片型号直接告诉你有多少le,xilinx也很贴心,虽然底层结构基于slice,但是等效换算成lc方便大家评估逻辑资源,spartan 6最大容量150k lc也是对标cyclone iv的150k le.紫光同创也是同样换算成等效的4输入lut。 细心的同学可能也发现c4是采用4输入lut,s6是采用6输入lut,为什么采用LUT5而不是流行的LUT6或LUT4? 仔细研究了下,发现CLM包括4个LUT5与6个DD,CLM的LUT5可以用mux开关互联,这样在一些需要更宽数据及多路输入的地方相当于lut4就可以实现同级互联用以减少传输delay,而采用lut6结构复杂度可能会增加,毕竟logos系列还是面向低成本、价格敏感型的项目,lut5的实现可能是综合考虑后的结构。 关于国产FPGA逻辑资源的介绍以及对比就先讲到这,下一节继续深入介绍。

|  /4

/4

/4

/4